# www.mientayvn.com

Dịch tiếng anh chuyên nghành khoa học tự nhiên và kĩ thuật.

Dịch các bài giảng trong chương trình học liệu mở của học viện MIT, Yale.

Tìm và dịch tài liệu phục vụ cho sinh viên làm seminer, luận văn.

Tại sao mọi thứ đều miễn phí và chuyên nghiệp ???

#### BÀI GIẢNG MÔN HỌC CÔNG NGHỆ VI ĐIỆN TỬ

Credits: 2

Prerequisites:- Semiconductor Devices

- Microelectronic Circuit Design

#### **REFERENCES**

- 1. HONG H. LEE, Fundamentals of Microelectronics Processing. 3<sup>rd</sup> Ed., McGraw-Hill; USA; 1990.

- 2. STEPHEN BROWN and ZVONKO VRANESIC, Fundamentals of Digital Logic with VHDL Design, 3rd Ed., Mc.Graw-Hill, 2000.

- 3. SUNG-MO KANG and YUSUF LEBLEBICI, *CMOS Digital Integrated Circuits Analysis and Design*. Mc.Graw-Hill, 2005.

- 4. DAN CLEIN, CMOS IC Layout, Newnes, 2000.

- 5. DAVID A. HODGES, HORACE G. JACKSON, RESVE A. SALEH, Analysis and Design of Digital Integrated Circuits in Deep Submicron Technology, Mc.Graw-Hill, 2003.

### CHƯƠNG 1. CƠ SỞ CÔNG NGHỆ MẠCH TÍCH HỢP

### §1.1 Các mạch tích hợp

Các mạch tích hợp (IC) là các mạch điện tử được chế tạo bởi việc tạo ra một cách đồng thời các phần tử riêng lẻ như transistor, diodes ... trên cùng một chip bán dẫn nhỏ (điển hình là Si), các phần tử được nối với nhau nhờ các vật liệu kim loại được phủ trên bề mặt của chip. Các vật liệu kim loại đóng vai trò như các " wireless wires". Ý tưởng này lần đầu tiên được đưa ra bởi Dummer năm 1952. Các mạch tích hợp đầu tiên được phát minh bởi Kilby, 1958.

Các mạch tích hợp về cơ bản được chia thành 2 loại chính: analog (hay linear) và digital (hay logic). Các mạch tích hợp tương tự hoặc khuếch đại hoặc đáp ứng các điện áp biến đổi. Tiêu biểu là các mạch khuếch đại, timers, dao động và các mạch điều khiển điện áp (voltage regulators). Các mạch số tạo ra hoặc đáp ứng các tín hiệu chỉ có hai mức điện áp. Tiêu biểu là các bộ vi xử lý, các bộ nhớ, và các microcomputer. Các mạch tích hợp cũng có thể được phân loại theo công nghệ chế tạo: monolithic hoặc hybrid. Trong khôn khổ giáo trình này chúng ta chỉ ngiên cứu loại thứ nhất.

Quy mô của sự tích hợp của các mạch tích hợp trên sơ sở Silicon đã tăng lên rất nhanh chóng từ thế hệ đầu tiên được chế tạo bởi Texas Instruments năm 1960 với tên gọi SSI (Small Scale Integration) đến thế hệ mới ULSI. Hiện nay công nghệ CMOS với minimum device dimension ( khoảng cách gate to gate) đạt tới cỗ vài chuc nm (0.65, 0.45).

Khuynh hướng chủ đạo trong việc giảm nhỏ kích thước linh kiện trong công nghệ mạch tích hợp là giảm chi phí cho cùng một chức năng, giảm tiêu thụ công suất và nâng cao tốc độ của linh kiện. Một khuynh hướng khác là vẫn tiếp tục sử dụng các đĩa bán dẫn lớn để giảm chi phí trên chip. Với cả hai khuynh hướng trên, công nghê xử lý vi điên tử luôn phải được cải tiến.

Các công nghệ IC chủ yếu hiện nay là công nghệ MOS và công nghệ BJT cho silicon và MES cho gallium arsenide.

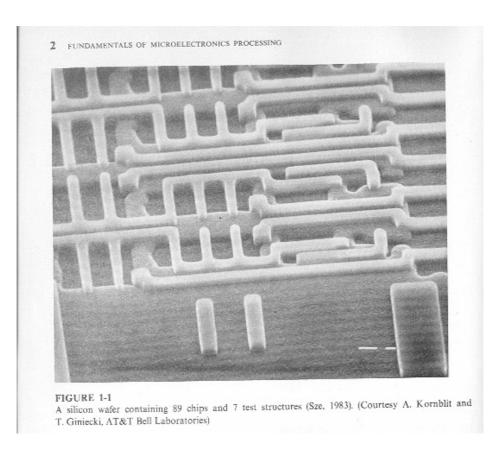

Hinh 1-1 (256 K DRAM, 1983, AT&T Bell Laboratories)

#### §1.2 Bán dẫn và các hạt tải

Si đơn tinh thể là vật liệu cơ sở cho công nghệ IC. Hình 1-2a mô tả một planar view của tinh thể Si với các điện tử của lớp ngoài cùng (lớp vỏ) trong các liên kết cong hóa tri (covalent bond) giữa các nguyên tử lân cân. Một chất bán dẫn có thể được định nghĩa như là một vật liệu có độ dẫn điện có thể điều khiển được, trong khoảng trung gian giữa điện môi và kim loại. Khả năng thay đổi độ dẫn của Si trong khoảng nhiều bậc có thể được thực hiện bởi việc đưa vào mang tinh thể Si các nguyên tử tạp chất hóa trị 3 như Boron hoặc hóa trị 5 như Phosphorus, chúng được gọi là các dopant hoặc là các tạp chất mong muốn. Quá trình này gọi là quá trình pha tạp hay doping. Các bán dẫn sạch được gọi là bán dẫn thuần hay intrinsic, các bán dẫn pha tạp gọi là extrinsic. Nếu pha tạp nhóm 5 (chẳng hạn P) vào Si thì ngoài 4 điện tử liên kết cọng hóa trị với 4 điện tử lớp vỏ của các nguyên tử Si lân cận, điện tử thứ 5 của nguyên tử tạp có liên kết lỏng lẻo với hat nhân và có thể chuyển đông tương đối dễ dàng trong mang tinh thế Si. Dạng bán dẫn này được gị là bán dẫn loại-n, và tạp nhóm 5 được gọi là tạp donor. Nếu pha tạp nhóm 3 (chẳng han B) vào Si thì 3 điện tử lớp vỏ của nguyên tử tạp liên kết cong hóa tri với các điện tử lớp vỏ của các nguyên tử Si lân cận do đó có thể coi lớp vỏ của nguyên tử tạp có 7 điện tử, và bị trống một điện tử. Vị trí liên kết khuyết này được gọi là một lỗ trống (hole). Một điện tử từ nguyên tử Si gần đó có thể "rơi" vào chỗ trống này và lỗ trống được xem như chuyển dời đến vị trí mới. Bán dẫn loại này được gọi là bán dẫn loại -p, và tạp nhóm 3 được gọi là tạp acceptor. Các điện tử và lỗ trống khi dịch chuyển sẽ mang theo chúng các điện tích âm và dương nên được gọi là các hạt tải. Các chất bán dẫn có thể ở dạng nguyên tố (như Si, Ge) hoặc hợp phần. Số điện tử trung bình trên một nguyên tử thường bằng 4, ngoại trừ trường hợp các bán dẫn A<sup>V</sup>-B<sup>VI</sup>.

Một bán dẫn thuần thường là điện môi trừ khi nó được kích thích nhiệt hoặc quang. Nếu kích thích đủ mạnh nó có thể trở thành dẫn điện. Các mức năng lượng khả dĩ của điện tử là rời rạc và sự kích thích sẽ làm cho các điện tử có thể nhảy lên mức năng lượng cao hơn. Vì chất bán dẫn có thể là điện môi hay dẫn điện tùy thuộc vào mức độ kích thích, nên có thể coi nó biểu hiện như một chất dẫn điện nếu năng lượng kích thích vượt quá một mức ngưỡng nhất định, gọi là energy barrier, ký hiệu  $E_{\rm g}$  (còn được gọi là khe năng lượng - energy gap). Khe năng lượng thay đổi từ  $0.18~{\rm eV}$  cho InSb tới  $3.6~{\rm eV}$  cho ZnS. Các vật dẫn như kim loại không có khe năng lượng nên có thể dẫn điện khi có hoặc không có kích thích. Các chất cách điện có khe năng lượng lớn đến mức không dẫn điện ngay cả khi kích thích mạnh. Khi

không có kích thích tất cả các điện tử của bán dẫn chiếm các mức năng lượng thấp trong các trạng thái hóa tri. Mặc dù các mức nặng lương là gián đoan nhưng vì có rất nhiều mức nên có thể xem tập hợp các trang thái cong hóa trị như một dải hay vùng hóa trị (valence band). Mức năng lương cao nhất của vùng hóa trị ký hiệu là E<sub>v</sub>. Phía trên khe năng lương (còn gọi là vùng cấm) là dải năng lương của các trang thái dẫn, gọi là vùng dẫn. Mức năng lượng thấp nhất của vùng dẫn ký hiệu là E<sub>c</sub>. Hình 1-2a mô tả cấu hình các mức năng lương của một bán dẫn thuần ở 0°K. Khi bán dẫn thuần được pha tạp donor, các điện tử donor sẽ chiếm các mức năng lương gần dưới vùng dẫn, với mức năng lương thấp nhất trong các mức này được gọi là mức donor, ký hiệu là  $E_d$  (hình 1-2b). Khi bán dẫn thuần được pha tạp acceptor, các lỗ trống sẽ chiếm các mức năng lượng gần trên đỉnh vùng hóa trị, với mức năng lượng cao nhất trong các mức này được gọi là mức acceptor, ký hiệu là E<sub>a</sub> (hình 1-2c). Khi bán dẫn thuần chịu kích thích nhiệt, một số điện tử trong vùng hóa trị bị kích thích có thể vượt qua vùng cấm để lên vùng dẫn đồng thời tạo ra một số lỗ trống tương ứng ở vùng hóa trị, và các cặp điện tử lỗ trống (EHP - electron hole pair) được tao ra. Vì các mức donor trong bán dẫn loại -n rất gần với vùng dẫn nên các kích thích nhe cũng đủ để làm cho các điện tử donor nhảy lên vùng dẫn, do đó nồng đô điện tử trong vòng dẫn là rất lớn ngay cả ở nhiệt đô thấp đối với việc hình thành các EHP. Với bán dẫn loại -p, vì các mức acceptor rất gần trên đính vùng hóa trị nên một kích thích nhẹ có thể làm cho các điện tử trong vùng hóa trị nhảy lên chiếm các mức acceptor và để lai các lỗ trống trong vùng hóa trị. Do đó các bán dẫn loại -p có thể có nồng đô lỗ trống lớn ngay cả ở nhiệt đô thấp.

Khi một bán dẫn được pha tạp loại-n hoặc loại -p, một trong hai loại hạt tải sẽ chiếm ưu thế về nồng độ và được gọi là hạt tải cơ bản (hay majority carrier), loại hạt tải còn lại được gọi là hạt tải không cơ bản (hay minority carrier).

## §1.3 Các quan hệ cơ bản và độ dẫn điện

Vì chuyển động của các hạt tải tạo ra sự dẫn điện, nên nồng độ hạt tải là đại lượng được quan tâm hàng đầu trong công nghệ IC. Với bán dẫn thuần, nồng độ điện tử trong vùng dẫn n bằng nồng độ lỗ trống trong vùng hóa trị p:

$$n = p = n_i \tag{1.1}$$

trong đó  $n_i$  gọi là nồng độ hạt tải nội của bán dẫn thuần ở trạng thái cân bằng (hay trạng thái tĩnh).

Giả thiết các tạp chất phân bố đồng nhất. Để thỏa mãn điều kiện trung hòa điện tích (trung hòa tĩnh điện) trong bán dẫn thuần, các điện tích dương phải bằng các điện tích âm. Với silicon, các tạp chất hoặc thiếu hụt hoặc dư thừa một điện tử so với Si. Vì vậy:

$$P + N_D = n + N_A \tag{1.2}$$

trong đó,  $N_D$  là nồng độ các nguyên tử donor và  $N_A$  là nồng độ các nguyên tử acceptor Phương trình (1.2) còn gọi là điều kiện trung hòa điện tích không gian, trong đó đã giả thiết rằng tất cả các điện tử donor và các lỗ trống acceptor đều được kích thích hoàn toàn sao cho các mức donor và acceptor đều hoàn toàn bị chiếm bởi các điện tử. Ở nhiệt độ phòng, giả thiết này nói chung có thể chấp nhận được trừ khi pha tạp quá mạnh (nồng độ nguyên tử tạp chất  $> 10^{18}$  cm<sup>-3</sup>). Nói cách khác,  $N_D$  có thể được thay thế bởi  $N_D^+$  và  $N_A$  bởi  $N_A^-$ .

Ở trạng thái cân bằng nhiệt:

$$pn = n_i^2 \tag{1.3}$$

Quan hệ này đúng cho các loại bán dẫn bất kỳ ở cân bằng nhiệt.

Với một bán dẫn loại -n, nồng độ điện tử  $n_n$  có thể nhận được khi thay (1.3) vào (1.2):

$$n_n = \frac{1}{2} \left\{ N_D - N_A + \left[ \left( N_D - N_A \right)^2 + 4n_i^2 \right]^{\frac{1}{2}} \right\}$$

(1.4)

Tương tự cho bán dẫn loại -p:

$$p_{p} = \frac{1}{2} \left\{ N_{A} - N_{D} + \left[ \left( N_{A} - N_{D} \right)^{2} + 4n_{i}^{2} \right]^{\frac{1}{2}} \right\}$$

(1.5)

Nồng độ hạt tải nội của Si là  $4.5 \times 10^{10}$  cm<sup>-3</sup> ở  $27^{\circ}$  C, của GaAs là  $9 \times 10^{6}$ . Độ lớn của nồng độ tạp chất tổng cọng  $|N_D - N_A|$  nói chung lớn hơn rất nhiều so với  $n_i$ . Vì vậy nồng độ hạt tải cơ bản có thể được tính xấp xỉ từ (1.4) và (1.5):

$$n_n \approx N_D - N_A \tag{1.6}$$

$$p_{p} \approx N_{A} - N_{D} \tag{1.7}$$

Nồng độ hạt tải không cơ bản (thiểu số) có thể được tính xấp xỉ từ (1.6), (1.7) và (1.3):

$$p_n \approx \frac{n_i^2}{N_D - N_A} \tag{1.8}$$

$$n_p \approx \frac{n_i^2}{N_A - N_D} \tag{1.9}$$

trong đó  $p_n$  và là nồng độ lỗ trống trong bán dẫn n và  $n_p$  là nồng độ điện tử trong bán dẫn p. Xác suất f(E) để một trạng thái điện tử với mức năng lượng E bị chiếm bởi một điện tử được cho bởi hàm xác suất Fermi-Dirac:

$$f(E) = \frac{1}{1 + e^{(E - E_F)/kT}}$$

(1.10)

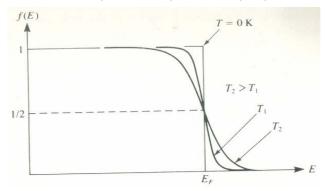

với T là nhiệt độ tuyệt đối, k là hằng số Boltzmann  $(8.62 \times 10^{-5} \text{ eV/K} = 1.38 \times 10^{-23} \text{ J/K})$  và  $E_F$  được gọi là mức Fermi. Mức Fermi chính là thế hóa học của điện tử trong chất rắn, và có thể xem như mức năng lượng mà tại đó xác suất chiếm trạng thái của điện tử đúng bằng 1/2. Đồ thị hàm phân bố xác suất Fermi-Dirac cho các nhiệt độ khác nhau được minh họa ở hình (1-3):

Hình 1-3 phân bố xác suất Fermi-Dirac

Từ hàm phân bố xác suất Fermi-Dirac, số khả dĩ các điện tử trong bán dẫn có mức năng lượng xác định có thể được tính từ hàm mật độ xác suất N(E). Nếu số trạng thái năng lượng trên một đơn vị thể tích (hay mật độ trạng thái) ở trong khoảng năng lượng dE là N(E)dE, thì số điện tử trên một đơn vị thể tích (hay mật độ điện tử) trong vùng dẫn, n, được cho bởi:

$$n = \int_{E_c}^{\infty} f(E)N(E)dE$$

(1.11)

Về nguyên tắc N(E) có thể được tính từ cơ học lượng tử và nguyên lý loại trừ Pauli. Tuy nhiên để tiện lợi có thể biểu diễn các điện tử phân bố trong vùng dẫn bởi  $m\hat{q}t$  độ  $hi\hat{q}u$  dụng các trang thái  $N_c$  định xứ tại bờ vùng dẫn  $E_c$ . Khi đó nồng độ điện tử trong vùng dẫn có dạng đơn gián:

$$N = N_c f(E_c) \tag{1.12}$$

Trong đó  $N_c$ được cho bởi:

$$N_{c} = 2 \left( \frac{2 \pi m_{n}^{*} kT}{h^{2}} \right)^{3/2}$$

(1.13)

$$= \begin{cases} 2.8 \times 10^{19} (T / 300)^{3/2} cm^{-3} \text{ for } Si \\ 4.7 \times 10^{17} (T / 300)^{3/2} cm^{-3} \text{ for GaAs} \end{cases}$$

trong đó  $m_n^*$  là khối lượng hiệu dụng của điện tử khi tính đến ảnh hưởng của mạng tinh thể lên đặc trưng của điện tử và h là hằng số Plank. Nếu ( $E_c$  -  $E_f$ ) lớn hơn một vài lần kT (thường ở nhiệt độ phòng kT = 0.026 eV nên điều kiện này thỏa mãn), thi phân bố xác suất  $f(E_c)$  có thể được tính gần đúng như sau:

$$f(E_c) = \frac{1}{1 + e^{(E_c - E_F)/kT}} \approx e^{-(E_c - E_f)/kT}$$

(1.14)

Khi đó (1.12) trở thành:

$$n = N_c e^{-(E_c - E_f)/kT}$$

(1.15)

Tương tự:

$$p = N_{v}e^{-(E_{f}-E_{v})/kT}$$

$$N_{v} = 2\left(\frac{2\pi m_{p}^{*}kT}{h^{2}}\right)^{3/2}$$

(1.16)

Với

$$= \begin{cases} 1.04 \times 10^{-19} \left( T / 300 \right)^{3/2} cm^{-3} & \text{for } Si \\ 7 \times 10^{-18} \left( T / 300 \right)^{3/2} cm^{-3} & \text{for } GaAs \end{cases}$$

(1.17)

$m_p^*$  là khối lượng hiệu dụng của lỗ trống. Các phương trình (1.15) và (1.16) có hiệu lực cho cả bán dẫn thuần và pha tạp, chỉ thay  $E_F$  bằng  $E_I$  cho trường hợp bán dẫn thuần.

Nếu các hạt tải phân bố đều, mật độ dòng điện do sự dịch chuyển của các điện tử với vận tốc  $\overline{V}_n$  trung bình theo một hướng nào đó (chẳng hạn hướng x) là:

$$J_n = qn \, \overline{v}_n \tag{1.18}$$

Nếu các hạt tải phân bố không đều thì còn có thêm thành phần dòng khuếch tán:

$$J_n = qn \, \overline{v}_n - D_n(q) \frac{dn}{dx} \tag{1.19}$$

Trong đó D là hệ số khuếch tán của hạt tải. Số hạng thứ nhất được gọi là dòng trôi (drift), tỷ lệ với cường độ điện trường E do vận tốc trung bình của các hạt tải tỷ lệ với cường độ điện trường E với hệ số tỷ lệ  $\mu$ , được gọi là độ linh động:

$$\overline{v} = \mu E; \qquad \mu \left[ \operatorname{cm}^2 / V.s \right]$$

(1.20)

Với điện tử:

$$\overline{v}_n = -\mu_n E$$

, với lỗ trống:  $\overline{v}_p = \mu_p E$

Độ linh động của hạt tải phụ thuộc vào nồng độ hạt tải và vào nhiệt độ. Nói chung độ linh động của điện tử lớn hơn độ linh động của lỗ trống. Với Si, ở nhiệt độ  $20^{\circ}$ C,  $\mu_n = 1900$  cm²/(V.s) và  $\mu_p = 425$  cm²/(V.s). Quan hệ (1.20) đúng với cường độ điện trường không quá lớn (thường nhỏ hơn 0.2V/cm). Với điện trường lớn hơn, độ linh động tăng chậm theo cường độ điện trường và tiến tới giá trị bão hòa. Dòng điện tổng cộng do cả hai loại hạt tải là:

$$J = J_{\rm n} + J_{\rm p}$$

(1.21)

Từ (1.19) dễ thấy rằng độ dẫn điện:

$$\sigma = q(n\mu_n + p\mu_p) \tag{1.22}$$

Hệ số khuếch tán trong (1.19) quan hệ với độ linh động theo hệ thức Einstein

$$D = \frac{kT}{q} \mu \tag{1.23}$$

### §1.4 Các đơn vị cơ sở của mạch tích hợp

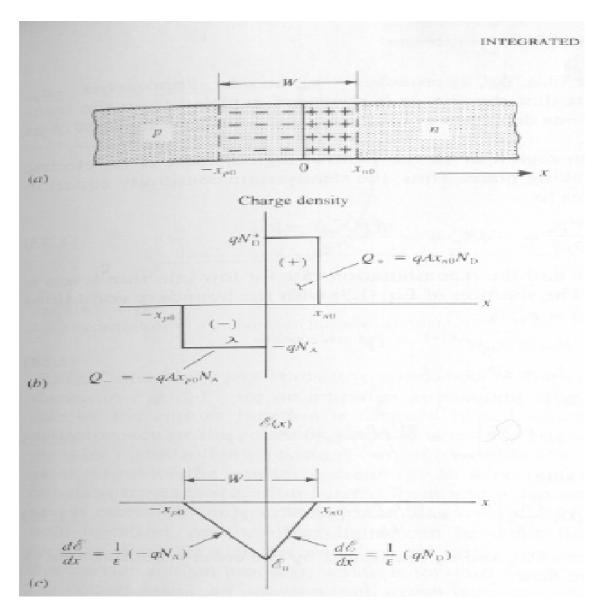

Các đơn vị cơ sở của Si-based Ics là MOSFET và BJT, và của GaAs-based ICs là MESFET. Một ứng dụng quan trọng của các tiếp xúc pn trong chế tạo IC là dùng để cách ly về điện cho nhiều loại phần tử tích cực. Với mục đích đó các tiếp xúc pn phải được áp đặt thế phân cực ngược hoặc bằng không. Ở chế độ này chiều cao rào thế sẽ tăng khi tăng nồng độ pha tạp.

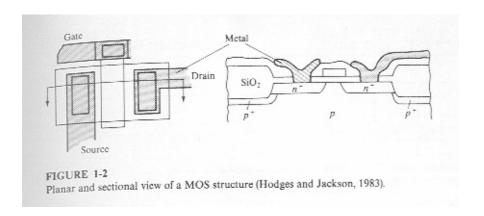

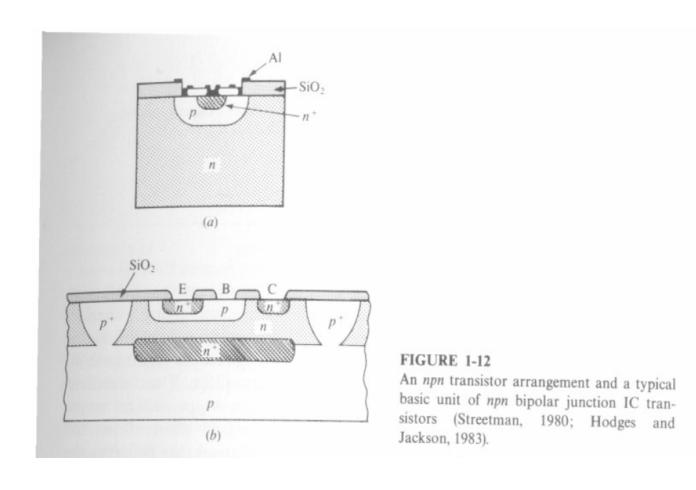

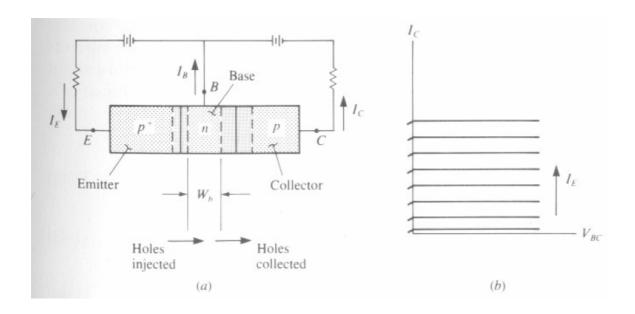

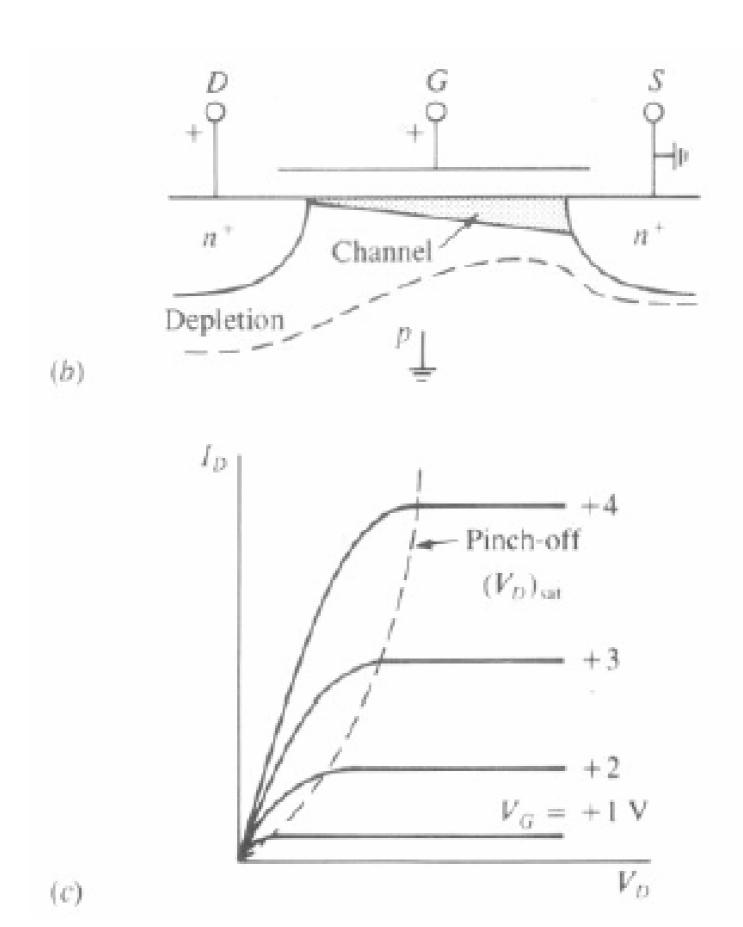

Các transistor có thể được dùng như các phần tử khuếch đại hoặc chuyển mạch. Trong cấu trúc ba lớp của BJT-transistor, lớp base (lớp giữa) rất mỏng và được pha tạp ít hơn so với emitter và collector. Vì vậy một dòng base rất nhỏ sẽ gây ra một dòng emitter-collector lớn hơn nhiều. Một BJT cách ly điển hình dùng cho các mạch tích hợp được mô tả ở hình (1.2).

Hình 1.2 Một đơn vị npn-BJT cơ bản dùng cho IC.

Vì cả ba cực đều phải ở trên bề mặt của chip, nên dòng collector phải chảy qua một đường dẫn có điện trở lớn trong vật liệu pha tạp nhẹ *n*. Một phương pháp chung để giảm điện trở collector là dùng một lớp pha tạp mạnh (n+) ngay bên dưới collector. Lớp n+ này được gọi là lớp ngầm (buried layer). Để cách

ly đơn vị BJT này với các đơn vị khác người ta dùng lớp để p để tạo ra các chuyển tiếp pn cách ly. Các BJT loại npn được dùng nhiều vì công nghệ chế tạo đơn giản hơn so với pnp-BJT.

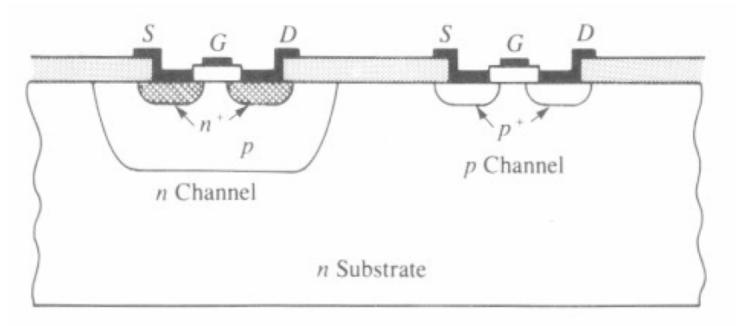

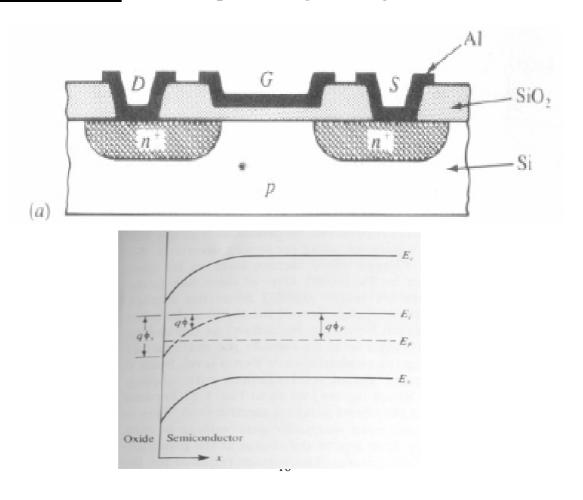

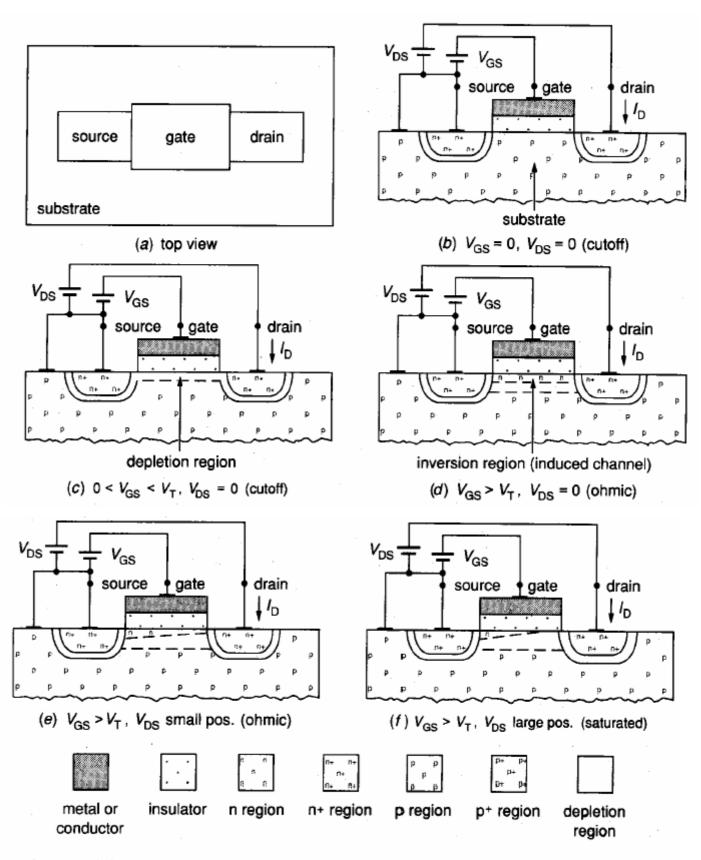

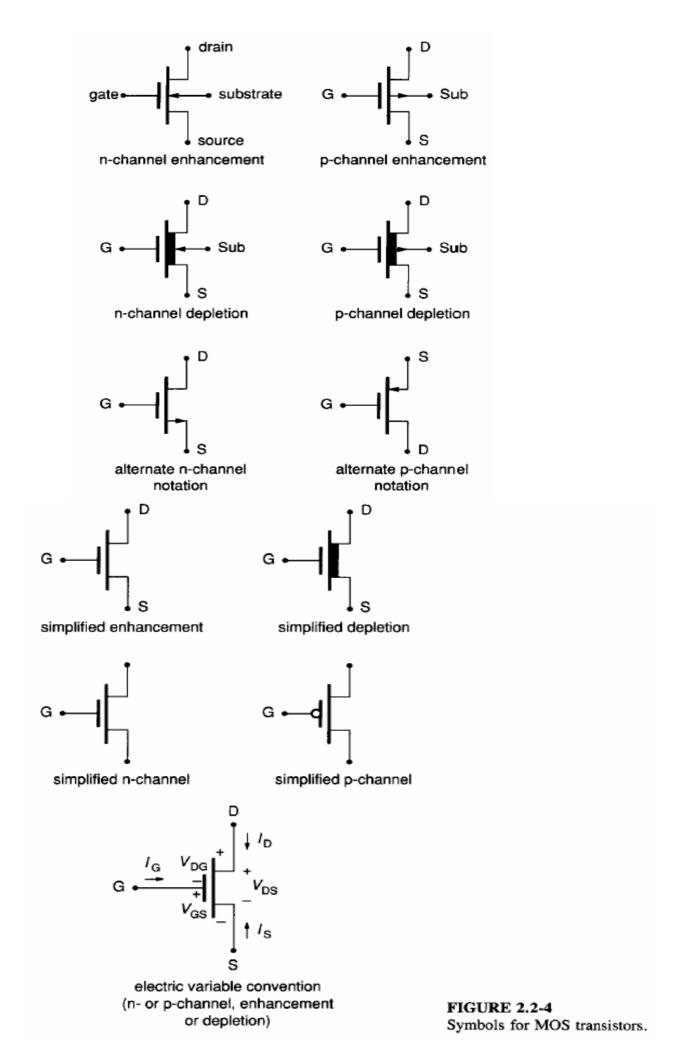

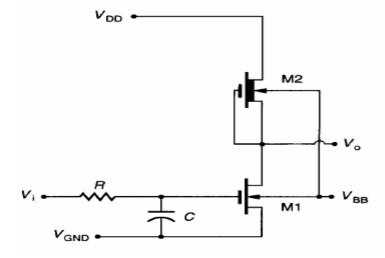

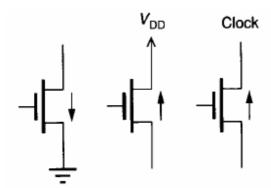

Transistor trường (FET) dựa trên công nghệ MOS chiếm ưu thế trong công nghệ IC, đặc biệt cho các IC logic. MOSFET có thể là kênh n hoặc kênh p tùy thuộc vào hạt tải cho sự dẫn điện là n hay p. Vì độ linh động của điện tử cao hơn nhiều so với lỗ trông nên MOSFET kênh n được dùng nhiều hơn. Một liên hợp có tính luân chuyển của NMOS và PMOS được gọi là CMOS (complimentary MOS), hình ( ).

Hình 1.3 Cấu hình CMOS đơn giản

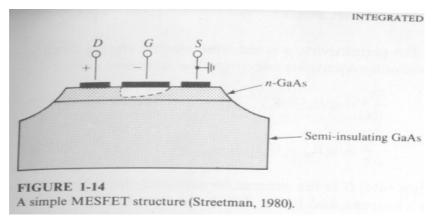

Do khó khăn trong công nghệ chế tạo cấu trúc MOS cho GaAs nên MESFET là cấu trúc cơ sở cho IC trên cơ sở GaAs. Tuy nhiên các MESFET-IC trên cơ sở GaAs có tốc độ cao, mật độ tích hợp cao và độ rộng vùng cấm lớn. Một cấu trúc đơn giản của MESFET trên cơ sở GaAs được mô tả ở hình ().

MESFET hoạt động với gate Schottky phân cực ngược và các tiếp xúc Ohmic cho drain và source. Đế là GaAs bán điện môi do pha tạp thích hợp, chẳng hạn Cl, sao cho mức Fermi được ghim ở gần giữa vùng cấm (do đó điên trở lớn).

# §1.5 Một số cơ sở vật lý linh kiện bán dẫn

Nồng độ hạt tải vượt trội tại các bờ vùng điện tích không gian:

$$\Delta p_n = p(x_{n0}) - p_{ne} = p_{ne} (e^{qV/kT} - 1)$$

$$\Delta n_p = n(-x_{p0}) - n_{pe} = n_{pe} (e^{qV/kT} - 1)$$

Phương trình Shockley

$$\Delta I_0 = \left(\frac{qD_p p_{ne}}{L_p} + \frac{qD_n n_{pe}}{L_n}\right) A$$

$$L_p = \left(D_p \tau_p\right)^{1/2}, L_n = \left(D_n \tau_n\right)^{1/2}$$

Dưới thế phân cực ngược (C-B), dòng ngược từ n to p chỉ phụ thuộc vào tốc độ tiêm lỗ trống p được điều khiển bởi chuyển tiếp pn (Emitter-Base) phân cực thuận.

$\rightarrow$  Good pnp Transistor cần gần như toàn bộ lỗ trống tiêm từ Emitter vào Base phải được góp vào Collector.  $\rightarrow$  Base cần đủ mỏng sao cho neutral length của Base  $W_b$  nhỏ hơn nhiều so với quãng đường khuếch tán của lỗ trống (không xảy ra tái hợp trong vùng Base). Đồng thời dòng điện

tử từ Base đến Emitter phải nhỏ hơn nhiều so với dòng lỗ trống từ E đến B.

→Pha tạp miền B thấp hơn miền E (p<sup>+</sup>n Emitter junction).

Các đại lượng quyết định tính năng của một BJT: hiệu suất tiêm Emitter, hệ số truyền đạt dòng, hệ số khuếch đại dòng base-collector.

$$\gamma \equiv \frac{I_{Ep}}{I_{En} + I_{Ep}}$$

$$\alpha \equiv \frac{I_{C}}{I_{E}} = \frac{I_{Ep}}{I_{E}} \frac{I_{C}}{I_{Ep}} = \gamma \frac{I_{C}}{I_{Ep}}$$

$$\beta \equiv \frac{I_{C}}{I_{R}} = \frac{\alpha}{1 - \alpha}$$

- Chỉ cần giải phương trình trung hoà cho miền Base vì các dòng được xác định bởi đặc trưng của hạt tải trong 2 miền chuyển tiếp quanh Base.

- Khi các thế phân cực lớn và Emitter pha tạp mạnh thì:

$$I_B = a_1 \tanh \left(\frac{W_b}{2L_p}\right)$$

$$I_C = a_1 \operatorname{csch} \left(\frac{W_b}{L_p}\right)$$

$$I_E = a_1 \coth \left(\frac{W_b}{L_p}\right)$$

$$a_{1} = \frac{qAD_{p}\Delta_{p_{E}}}{L_{p}}, \Delta_{p_{E}} = p_{Be}(e^{qV_{EB}/kT} - 1)$$

$L_p$  là chiều dài khuếch tán trong miền Base và  $p_{Be}$  là nồng độ lỗ trống cân bằng trong miền Base.

- Ba yếu tố quan trọng:

- Thế phân cực (số hạng exp(qV/kT)

- Các dòng Emitter và Collector được xác định bởi gradient nồng độ hạt tải không cơ bản tại biên của chuyển tiếp.

- Dòng Base bằng hiệu dòng Emitter và Collector

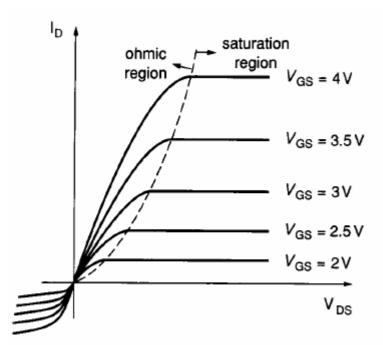

# Cấu trúc MIS: đặc biệt quan trọng cho digital ICs.

Đặc trưng I-V:

$$I_D = \frac{\overline{\mu}_n ZC_i}{L} \left[ \left( V_G - V_T \right) V_D - \frac{1}{2} V_D^2 \right]$$

Z: chiều sâu của kênh, L: chiều dài kênh,  $C_i$ : điện dung lớp cách điện trên đơn vị diện tích,  $\overline{\mu}_n$  độ linh động bề mặt của điện tử.

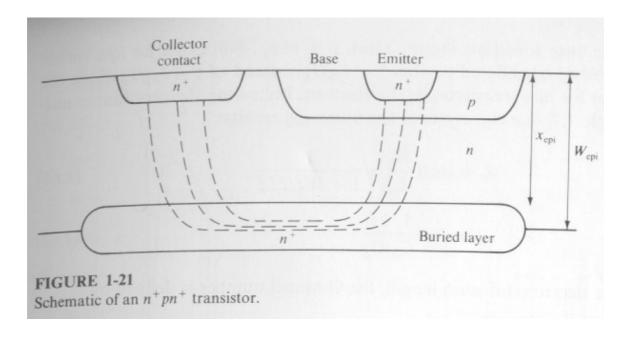

## §1.6 Ví dụ thiết kế BJT

Phần này sẽ xem xét một thiết kế cho việc chế tạo một BJT với một lớp ngầm như đã nói tới ở phần trước. Tuần tự thiết kế và chế tạo chưa được đề cập ở đây. Hình (1.6.1) là sơ đồ của một n+pn+ BJT.

Các thông số quan trọng là hệ số khuếch đại dòng base-collector,  $\beta$ , tần số cư toff, là tần số ứng với sự suy giảm của hệ số khuếch đại ac về đơn vị, tần số cắt alpha,  $f_{\alpha}$ , liên quan với thời gian dịch chuyển của hạt tải thứ yếu qua miền base  $\tau_B$ , tương ứng với sự suy giảm 3 dB của độ lợi so với giá trị của nó ở tần số thấp:

$$f_{\alpha} = 1/(2\pi\tau_B)$$

và:

$$\tau_B = \frac{W_b^2}{\eta D_n}$$

trong đó η là hệ số phụ thuộc vào mức pha tạp (=2 cho base pha tạp đồng nhất), và vào điện trường áp đặt.

Ngoài ra còn có hai tiêu chuẩn cho sự hoạt động bình thường của transistor. Một là thế đánh thủng. Dưới điều kiện phân cực ngược, có hai nguyên nhân gây ra hiện tượng đánh thủng. Một là tunnel do điện trường cảm ứng (thường giữa hai miền pha tạp mạnh, hiệu ứng Zener). Hai là đánh thủng thác lũ, do các cặp điện tử-lỗ trống được tạo ra do các hạt tải được gia tốc bởi điện trường. Thế đánh thủng (BV) thường liên quan với hệ số nhân collector như sau:

$$M = \frac{1}{1 - \left[V_{CB} / (BV)_{CB^{\circ}}\right]^n}$$

Trong đó n là hằng số và  $(BV)_{Cbo}$  là thế đánh thủng hở mạch. Độ lợi dòng  $\alpha$  được biểu diễn bởi:

$$\alpha = \frac{I_C}{I_E} = \frac{I_C}{I_{Cn}} \frac{I_{Cn}}{I_{En}} \frac{I_{En}}{I_E} = M \alpha_T \gamma$$

Trong đó  $\alpha_T$  là hệ số vận chuyển base,

$$\alpha_T \approx \operatorname{sech} \frac{W_b}{L_n} \approx \frac{1}{1 + W_b^2 / 2L_n^2}$$

$$\gamma \approx \frac{1}{1 + G_B / G_E}$$

Trong đó  $L_n$  là quãng đường khuếch tán của điện tử, số Gummel  $G_B$  được xác định bởi:

$$G_{B} = \frac{1}{D_{nB}} \int_{base} N_{B}(x) dx = \frac{Q_{Bo}/q}{D_{nB}}$$

(1.6.1)

và  $G_E$  được xác định tương tự cho emitter,  $Q_{Bo}$  là điện tích tiếp xúc của base. Dấu xấp xỉ ứng với điều kiện  $W_b>> L_n$ .

$$\beta \approx \frac{1}{G_B / G_E + W_b^2 / 2L - \left[V_{CB} / (BV)_{CBo}\right]^n}$$

Nếu giả thiết có một phân bố Gauss của nồng độ tạp chất (kết quả của  $\mathring{u}$  nhiệt), với nồng độ tại bề mặt là  $N_{Bo}$  thì:

$$N_B = N_{Bo} e x p(-\frac{x^2}{4Dt}) - N_C$$

Với  $N_C$  là nồng độ tạp ở collector (bên phía base của chuyển tiếp collector-base), khi đó:

$$\frac{Q_{Bo}}{q} = \left(\frac{Dt}{2}\right)^{1/2} N_{Bo} \left(\int_{0}^{t_2} e^{-y^2/2} dy - \int_{0}^{t_1} e^{-y^2/2} dy\right) - \int_{x_{EB}}^{x_{CB}} N_C dx$$

Với

$$t_1 = \frac{x_{EB}}{\left(2Dt\right)^{1/2}}$$

$$t_2 = \frac{x_{CB}}{\left(2Dt\right)^{1/2}}$$

Trong đó  $x_{EB}$  và  $x_{CB}$  là khoảng cách từ bề mặt tới mép của các miền emitter-base và collector-base tương ứng. Khi đó:

$$(BV)_{CBo} = \frac{q}{\varepsilon_{S}} \left( \frac{Q_{Bo} x_{1}}{q} - \frac{N_{C} x_{1}^{2}}{2} + \frac{Q_{Bo} W_{b}}{2q} \right)$$

(1.6.2)

$$V\acute{o}i \; x_1 = x_{epi} - x_{BC}$$

Các phương trình (1.6.1 và 1.6.2) dùng để xác định công nghệ chế tạo. Vấn đề có thể được phát biểu dưới dạng: cho các giá trị mong muốn của  $\beta$ ,  $f_T$ ,  $(BV)_{CBo}$ , và  $R_{SB}$  (trở kháng sheet của base), cần xác định kích thước và cách thức pha tạp cho việc chế tạo BJT như hình (1.6.1). Bài toán và lời giải được tóm tắt trong bảng sau.

#### Design specifications for the example (Colclaser, 1980) $\omega_n = 2\pi \times 5 \times 10^9 \text{ rad/s}$ Design values: $\beta_F = 45$ $R_{sB} = 200 \Omega/\Box$ $(BV)_{CBo} = 25 \text{ V}$ $x_{\rm epi} = 3.1 \ \mu \rm m$ $W_{\rm epi} = 6.4~\mu{\rm m}$ Dimensions: $x_{iE} = 0.67 \ \mu m$ $x_{ic} = 1.45 \ \mu m$ Buried layer $R_s = 25 \Omega/\Box$ $x_B = 0.49 \ \mu \text{m}$ $N_o$ , cm<sup>-3</sup> $R_*, \Omega/\square$ Diffusion processes T, °C t, min

39

60

17.4

23.4

47.8

50

200

$\sim 20$

950

1200

900

1100

950

$1.55 \times 10^{20}$

$5.5 \times 10^{18}$

$1.2 \times 10^{20}$

$6.5 \times 10^{18}$

$8.4 \times 10^{20}$

Isolation

Base

Predeposit

Predeposit

Drive-in

Emitter

Drive-in

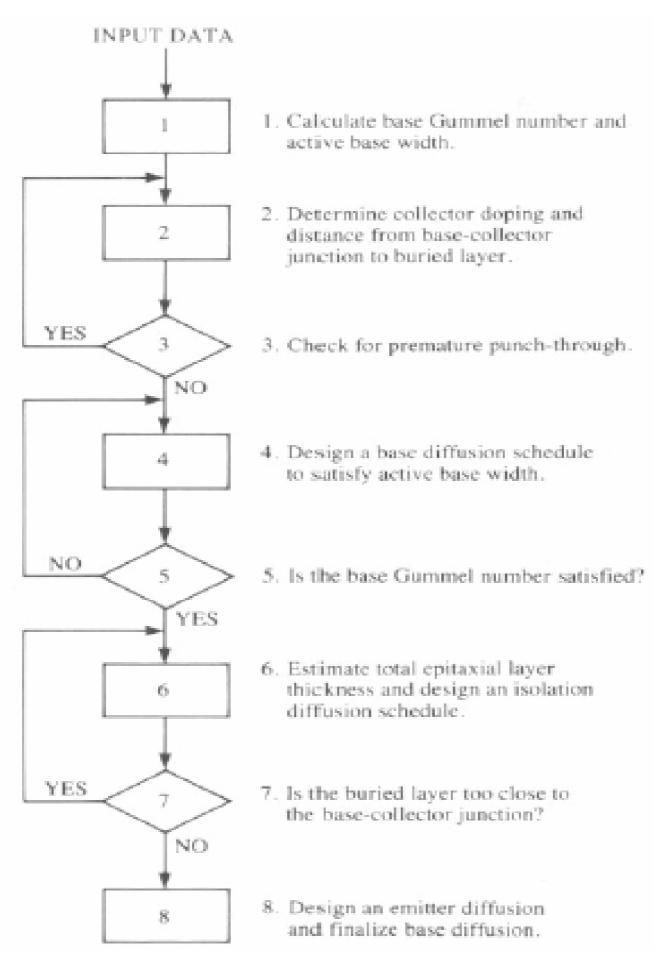

Lưu đồ thuật toán cho bài toán

chế tạo:

1. Chọn một giá trị tiêu biểu của  $G_E$  ( $5x10^{13}$  cm<sup>-4</sup>). Giả thiết  $\beta$  thỏa mãn (có thể kiểm tra lại sau), tính  $G_B$ :

$$G_B = G_E/\beta = 5x10^{13}/45 = 1.11x10^{12} \ cm^{\text{-4}} s$$

Nồng độ pha tạp trung bình ở base thường là  $10^{17}$  cm<sup>-3</sup>.

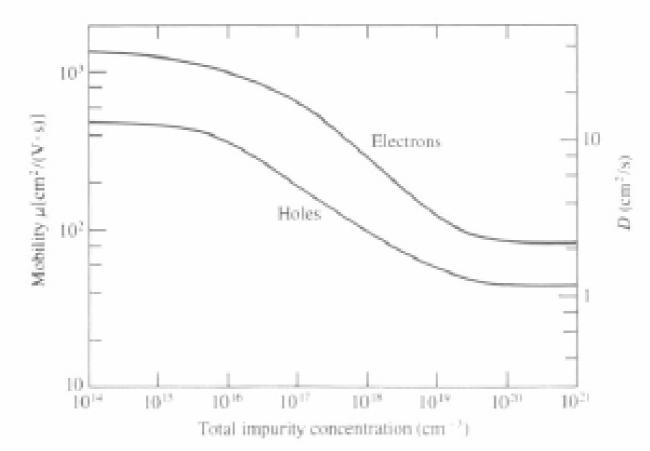

FIGURE 1-7

Mobility as a function of total dopant concentration (Grove, 1967).

Từ hình 1-7 đọc được  $D_{nB}$  là 15 cm²/s. Từ (1.63) suy ra:

$$Q_{Bo}/q = D_{nB}G_B = 1.67x10^{13} \text{ cm}^{-2}$$

Từ 1.57 và 1.58 với  $\eta = 4$  và giải cho  $W_b$  suy ra:

$$W_b = (\eta D_{nB}/2\pi f\alpha)1/2 = 0.49 \ \mu m$$

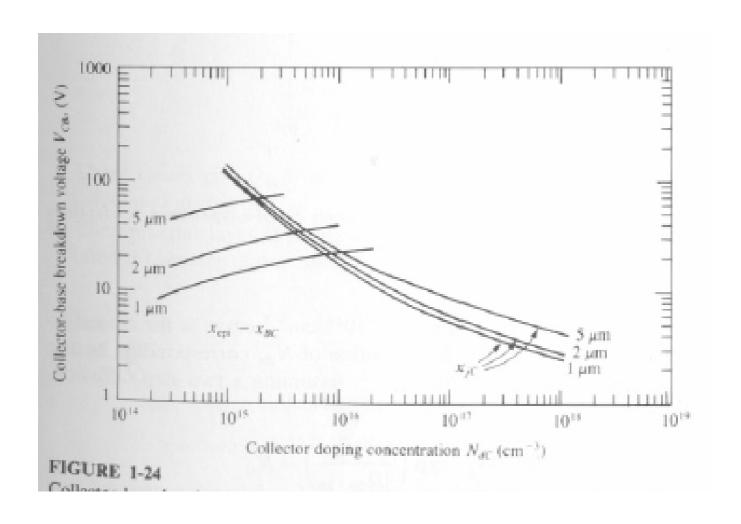

2. Giả thiết chuyển tiếp base-collector định xứ ở khoảng 2  $\mu$ m tính từ bề mặt  $(x_{jC})$ , thế đánh thủng  $(BV)_{Cbo} = 25$  V, khi đó dùng hình 1-24 để tìm ra:

$$X_{epi}$$

-  $x_B = x1 \approx 1.2 \ \mu m$

Nồng độ pha tạp collector tối đa cho phép là  $N_{\rm C} = 8 {\rm x} 10^{15} \ {\rm cm}^{-3}$

Hình 1-24

3. Kiểm tra thế punch - through sử dụng (1.6.2):  $(BV)_{Cbo} = 372 \text{ V. Vì}$  giá trị đã chọn là 25 V nên có thể chuyển sang bước 4

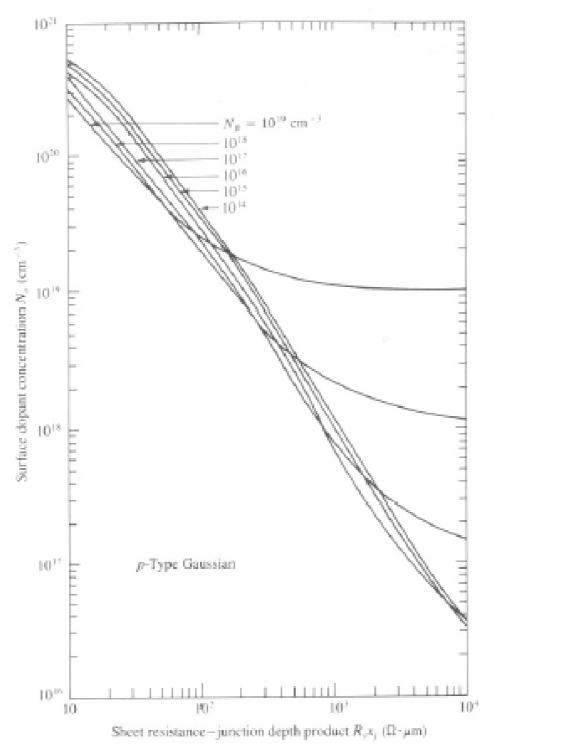

4. Với quá trình khuếch tán nhiệt theo phân bố Gauss, dùng hình 1-25 để nhận được giá trị  $N_{\rm bo}$ .

FIGURE 1-25

Surface dopant density of a p-type Gaussian diffusion in uniformly doped n-type silicon as a function of average resistivity at 300 K (Irvin, 1962).

Trong hình 1-25, đường  $N_B=10^{16}~\text{cm}^{-3}$  gần với giá trị của  $N_C$  đã tính từ bước 2. Giá trị tìm được là  $N_{bo}=4x~10^8~\text{cm}^{-3}$ . Giả thiết quá trình khuếch tán là 2 -step, chuyển tiếp xảy ra khi

$$N(x_j,t) = N_{bo} \exp(-x_{jC}^2/4D_{2B}t_{2B}) = N_C$$

Hoặc  $D_{2B}t_{2B} = 1.6x10^{-9} \text{ cm}^2$ .

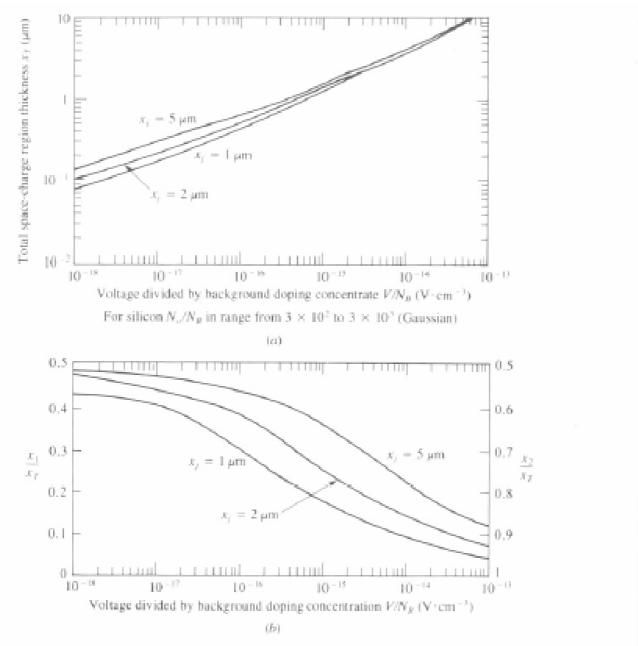

#### FIGURE 1-26

Space-charge region thickness as a function of voltage for a pn junction formed by a Gaussian diffusion into a constant background concentration: (a) total width  $x_T$  and (b) ratios  $x_1$  and  $x_2$  where  $x_1$  is the portion in the heavier doped side and  $x_2$  is that in the lighter doped side (Lawrence and Warner, 1960).

5. Bây giờ giá trị  $Q_{bo}/q$  đã tính từ trước có thể được kiểm tra nhờ hình 1-26 cho độ rộng của vùng điện tích không gian base - collector  $(x_T)$  và các độ rộng tương ứng của các miền pha tạp mạnh  $(x_1)$  và pha tạp nhẹ  $(x_2)$ . Nếu giá trị tính được nhờ hình 1-26 lớn hơn giá trị đã tính trước, thì  $x_{jC}$  phải tăng và bước 4 được lặp lại cho đến khi điều kiện trên thỏa mãn. Với chuyển tiếp chưa bị áp đặt thế phân cực thì  $V = 0.7 \ V$ . Khi đó :

Độ rộng toàn bộ miền điện tích không gian =  $0.5 \mu m$

Phía base =  $0.19 \mu m$

Phía collector =  $0.31 \mu m$

Các biên của base tích cực,  $x_{CB}$  và  $x_{EB}$  là:

$$x_{CB} = 2 - 0.19 = 1.81 \ \mu m$$

$$x_{EB} = x_{CB}$$

-  $W_b = 1.81$  -  $0.49 = 1.32~\mu m$

Dùng 1.66 cho kết quả:  $Q_{bo}/q = 5.3 \times 10^{12}$  cm-2, Giá trị này nhỏ hơn giá trị 1.67 x  $10^{13}$  đã nhận được từ bước 1. Do đó lặp lại các bước 4 và 5 cho các giá trị:

$$x_{jC} = 1.45 \ \mu m$$

$$D_{2B}t_{2B} = 7.85 \text{ x } 10^{-10} \text{ cm}^2$$

$$N_{bo} = 6.5 \times 10^{18} \text{ cm}^{-3}$$

Các giá trị này cho kết quả  $Q_{bo}/q=1.66 \ x \ 10^{13} \ cm^{-2}$ , rất gần với giá trị đã tính ở bước 1.

6. Chiều dày lớp epitaxi  $W_{epi}$  và xepi có thể được tính. Từ bước 2 có:

$$X_{epi}$$

-  $x_{BC}$  = 1.2  $\mu m$

Và  $x_{BC} = x_{jC} + d$ ộ rộng phía collector của chuyển tiếp B-C  $= 1.45 + 0.31 = 1.76 \ \mu m$

Do đó  $x_{epi} = 1.2 + 1.76 = 2.96 \mu m$ . Nếu giả thiết sự phủ trước của lớp ngầm vào lớp epitaxi trong quá trình epitaxi, thì:

$$0.9W_{eni} = X_{eni} + X_2$$

với  $x_2$  là chiều sâu thâm nhập của lớp ngầm vào lớp epitaxi trong quá trình khuếch tán cách ly. Để thử nghiệm, đặt  $x_2=2$  µm, khi đó  $W_{\rm epi}=5.5$  µm. Giả thiết điện trở sheet khuếch tán cách ly là 50  $\Omega/\Box$ , nồng độ bề mặt  $N_{\rm io}(N_{\rm co})$  là 7 x  $10^{18}$  cm<sup>-3</sup> (từ hình 1-25). Dùng giá trị này cùng với phân bố Gauss có thể tính  $X_2=2.44$  µm.

7. Giá trị tính được của  $x_2$  lớn hơn giá trị thử ( $2\mu m$ ). Điều này chứng tổ lớp ngầm quá gần chuyển tiếp B-C và do đó bước 6 được lặp lại. Các giá trị mới là:

$$W_{epi} = 6.4 \mu m$$

$$X_{epi}=3.1\ \mu m$$

$$N_{io} = 5.5 \times 1018 \text{ cm}^{-3}$$

8. Vị trí tính từ bề mặt của chuyển tiếp emitter, x<sub>jE</sub> cần phải được xác định. Phần base của miền B-E dưới thế phân cực thuận là xấp xí 0.1 μm. Khi đó:

$$X_{jE} = x_{jC}$$

-  $x_{CB}$  -  $W_b$  -0.1

$$= 1.45 - 0.19 - 0.49 - 0.1 = 0.67 \ \mu m$$

Cuối cùng, nồng độ tạp tổng cộng tại  $x_{jE}$  phải bằng 0. Điều này ngụ ý rằng:

$$\boldsymbol{N}_{E}(\boldsymbol{x}_{jE}) = \boldsymbol{N}_{B}(\boldsymbol{x}_{jE})$$

-  $\boldsymbol{N}_{C}(\boldsymbol{x}_{jE})$

Hay

$$N_E = N_{bo} \exp(-x_{iE}^2/4D_{2B}t_{2B}) - N_C = 1.55 \times 10^{18} \text{ cm}^{-3}$$

Phương trình này có thể dùng để quyết định thủ tục pha tạp.

## §1.7 Các giai đoạn chính của qui trình chế tạo vi điện tử

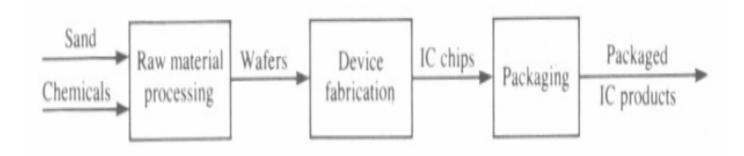

Hình () mô tả các quá trình cơ bản của công nghệ chế tạo IC, bao gồm quá trình tinh chế vật liệu, quá trình mọc tinh thể và chuẩn bị các wafer trên đó IC được chế tạo, quá trình chế tạo linh kiện (IC), quá trình đóng kiện, lưu giữ và kiểm tra. Mặt sau của các chip (die) được gắn cơ học hoặc nôi với môi trường gá giữ thích hợp, thường là plastic hoặc ceramic.

FIGURE 1-27

A broad view of microelectronics processing.

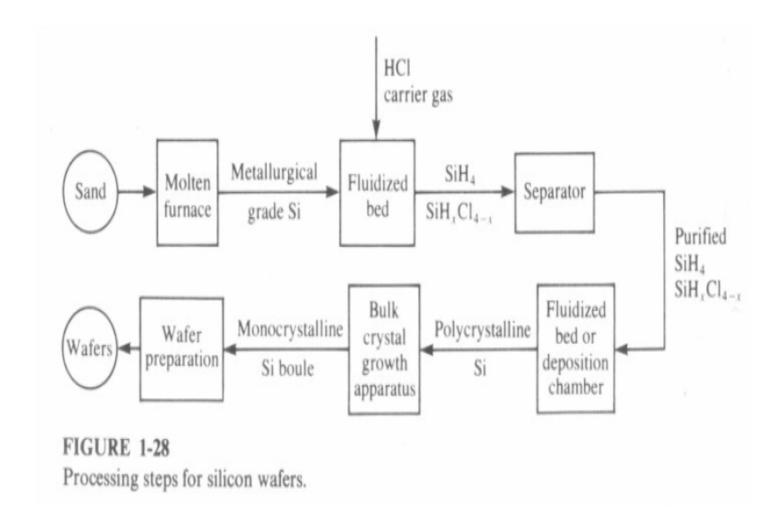

Các wafer thường là các đĩa mỏng (chẳng hạn 0.5 mm với Si) của vật liệu đơn tinh thể pha tạp donor hoặc acceptor. Yêu cầu độ sạch của tạp và dộ hoàn hảo của cấu trúc tinh thể là rất nghiêm ngặt. Một qui trình xử lý têu biểu được mô tả ở hình 1-28.

Vật liệu khởiđầu có thể là cát hoặc một khoáng chất của Si. Một lò hồ quang điện nóng chảy được dùng để tạo ra Silic có độ sạch cấp luyện kim (metallurgical grade silicon, MGS), độ sạch khoảng 98%. Các hạt MGS được đưa vào lò phản ứng lỏng với một khí tải chứa hydrochloric acid để chuyển MGS thành các khí chứa Si như silane và chlorosilane. Các khí được tách và làm sạch qua một dãy các bộ tách và chưng cất. Có hai phương pháp chính để tạo ra Si sạch cấp độ điện tử (electronic grade,

EGS). Một phương pháp bao gồm sự phủ Si từ khí chứa Si lên trên một ống Si nóng (ống Si nóng tạo ra các vị trí kích cỡ nguyên tử). Ông Si lớn rất nhanh đến đường kính 20 cm. Nếu dùng khí trichlorosilane, thì phản ứng xảy ra như sau:

$$SiHCl_3(gas) + H_2(gas) \rightarrow Si(solid) + 3HCl(gas)$$

Phương pháp thứ hai, có nhiều ưu điểm hơn, sử dụng phản ứng trong bể lỏng. Trong đó khí chứa Si và các hạt mầm Si tinh khiết được nuôi. Si EGS có cấu trúc đa tinh thể và chứa tạp chất có nồng độ trong khoảng ppm (nhỏ hơn 20 ppm). Tiếp theo Si EGS sẽ được cho nóng chảy để nuôi thành thỏi đơn tinh thể.

Có 3 phương pháp chính để nuôi thỏi đơn tinh thể từ Si EGS. Phương pháp được sử dụng rộng rãi nhất là kỹ thuật Czochralski. Trong phương pháp này, một hạt đơn tinh thể mầm nhỏ được nhúng trong EGS nóng chảy, và tinh thể mầm sẽ được kéo gradual sao cho thỏi đơn tinh thể được có đường kính 15 cm được hình thành từ quá trình làm nguội. Một phương pháp khác là phương pháp nóng chảy vùng. Trong phương pháp này, một thỏi Si đặt theo phương thẳng đứng được làm nóng chaỷ cục bộ từ dưới lên sử dụng lò cục bộ quét từ dưới lên (chẳng hạn lò vi sóng). Vùng nóng chảy được tái tinh thể hóa nhờ các tinh thể mầm. Phương pháp thứ ba là phương pháp Bridgeman, được dùng chủ yếu cho GaAs. Trong đó vật liệu đa tinh

thể được làm nóng chảy dọc theo một thuyền hẹp, dài nhờ lò quét dọc. Và được làm nguội từ một phía có gắn với tinh thể mầm.

Quá trình nuôi đơn tinh thể có hai mục tiêu. Một là chuyển cấu trúc đa tinh thể thành cấu trúc đơn tinh thể. Hai là loại bỏ các tạp chất không mong muốn. Quá trình này xảy ra ở mặt phân cách rắn - lỏng. Trong quá trình nuôi đơn tinh thể, các tạp chất có thể được đưa vào để tạo ra đơn tinh thể bán dẫn loại n hoặc p. Các thỏi bán dẫn sẽ được cắt thành các phiến mỏng, đường kính 0.5 mm (wafer). Mặc dù chỉ một phần rất mỏng của đĩa bán dẫn được dùng để tích hợp linh kiện, nhưng độ dày của đĩa bảo đảm cho sự ổn định cơ học của IC.

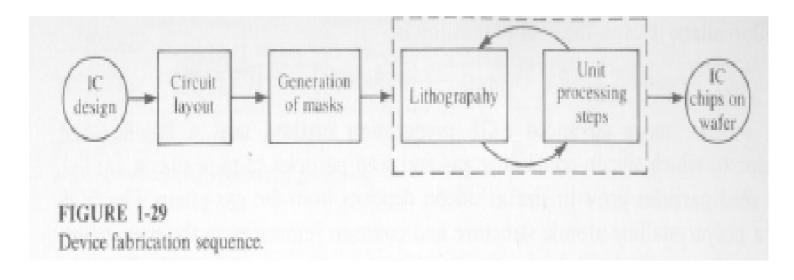

So với công nghệ chế tạo wafer thì công nghệ chế tạo linh kiện phát triển nhanh hơn nhiều. Một số công nghệ có thể trở thành lạc hậu trước khi được công bố. Tuy nhiền nền tảng và mục tiêu của chúng có thể chưa thay đổi.

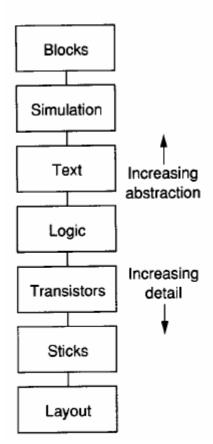

Hình 1-29 mô tả các bước tuần tự của qui trìnhchế tạo IC. Khi cho trước các yêu cầu và các chi tiết kỹ thuật của mạch thì IC có thể được thiết kế dưới dạng circuit layout với các chi tiết về chiều rộng, chiều sâu của mỗi một đơn vị cơ bản. Chẳng hạn với một MOSFet đơn giản, sơ đồ bố trí tổng thể (layout) sẽ được chuyển thành các sơ đồ khổ lớn cho mỗi một mức mặt nạ. Sau đó các sơ đồ này sẽ được thu nhỏ lại để thu được mặt nạ cuối cùng. Với các mạch VLSI, người thiết kế có thể mô tả một cách điện tử toàn bộ layout của mạch. Sau đó thiết kế được chuyển thành dạng số và được lưu trữ trên băng từ. Mặt nạ có thể bao gồm nhiều mức khác nhau cho các chế tạo khác nhau. Các mặt nạ được làm từ các vật liệu như chromium, chromium oxide, hoặc silicon.

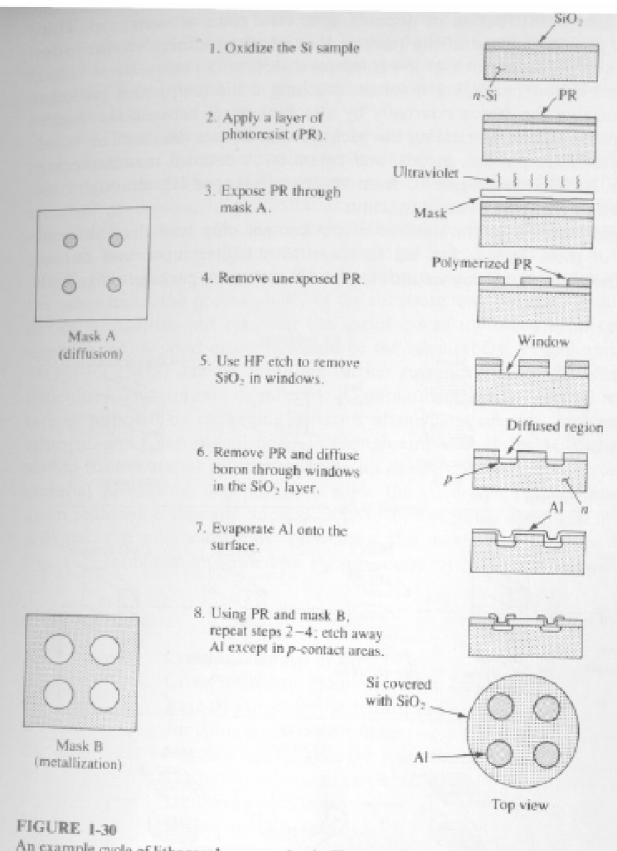

An example cycle of lithography processing in Fig. 1-29 (Streetman, 1980).

Bước tiếp theo là quá trình quang khắc (lithography), có thể được lặp lại nhiều lần cho các bước xử lý tương ứng với các mức mặt nạ khác nhau. Quang khắc là quá trình chuyển dạng hình học trên mặt nạ vào bề mặt của Si wafer. Mỗi chu trình quang khắc thường bao gồm sự ăn mòn qua các cửa sổ mở hoặc vạch các dạng nhất định cho bước tiếp theo, chẳng hạn như phủ các màng mong muốn hay đưa tạp chất vào các vùng đã được mở nhờ quá trình khuếch tán hoặc cấy ion. Các bước tiêu biểu của quá trình quang khắc được mô tả trong hình 1-30. Các mặt nạ được dùng để mở các cửa số qua lớp silicon dioxide sao cho tạp chất dưới dạng khí có thể khuếch tán qua đó. Một lớp cản quang (photoresist, PR) từ các vật liệu polymer nhạy sáng được phủ lên trên mặt lớp SiO2. Mặt nạ được đặt ên trên lớp PR và được chiếu tia cực tím. Các chỗ lộ sáng sẽ bị polymer hóa, còn các chỗ bị thì không. Các vùng không bị polymer hóa sẽ bị ăn mòn bởi acid BHF (buffered-HF), để lộ ra các cửa sổ cho quá trình khuếch tán. Các wafer sẽ được đặt vào lò để khuếch tán có chưa khí tải B2H6 hoặc PH3để tạo ra các miền pha tạp mong muốn.

Các bước xử lý đơn vị tiêu biểu bao gồm sự phủ màng epitaxi (đơn tinh thể) và màng không epitaxi, sự oxi hóa, cấy ion và kim loại hóa (phủ kim loại). Quá trình này nhằm mục tiêu tạo ra các miền tích cực và cách ly chúng với nhau. Yếu tố chính ở đay là sự phân bố tạp chất và sự mô tả rõ

ràng của phân bố tạp chất. Các wafer phải trải qua nhiều bước khác nhau của quá trình xử lý ở nhiệt độ cao nên có thể dẫn tới sự phân bố lại tạp chất. Do đó rất nhiều nỗ lực đã được thực hiện để hạ thấp nhiệt độ của các quá trình xử lý.

Quá trình đóng kiện mạch IC bao gồm việc gắn chip (die) vào một vật liệu gá nhất định, việc nối dây giữa các đường dẫnlinh kiện với gá và tạo hình cho nó. Các vật liệu gá thường là plastic, kim loại và gốm.

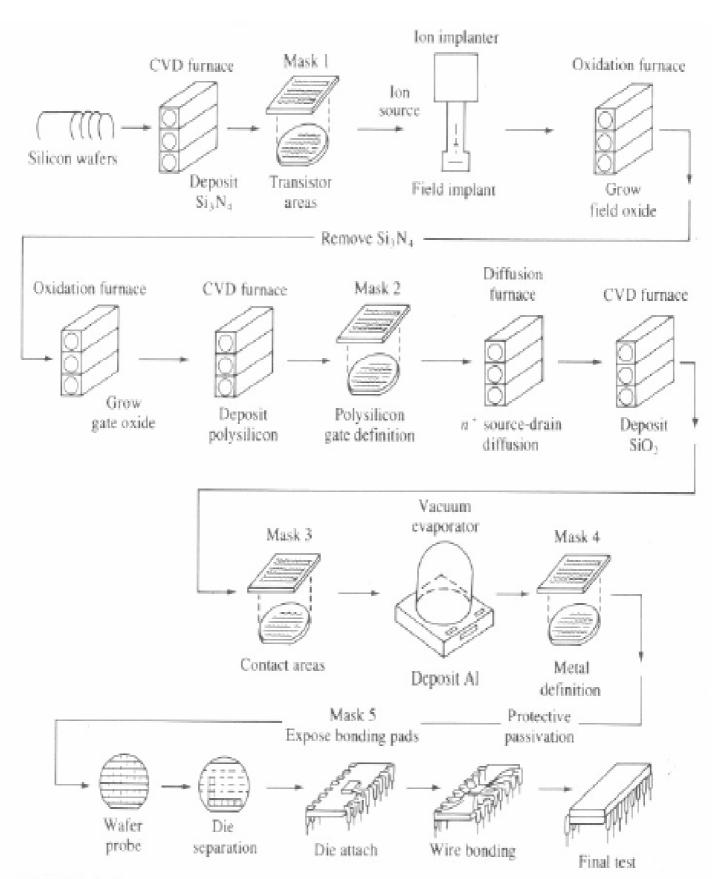

Hình 1-31 mô tả quá trình chi tiết chế tạo một NMOS Si - gate IC từ các wafer ban đầu đến đóng kiện cho IC. Khi mật độ linh liện tăng lên thì số chân của IC trở thành một nhược điểm do kích thước bộ gá lớn sẽ làm tổn hao nhiệt lớn. Đồng thời số chân của IC nhiều cũng làm tăng tín hiệu nhiễu. Bên cạnh đó thời gian sử dụng (lifetime) cũng là một yếu ttó quan trọng trong việc thiết kế gá giữ IC.

FIGURE 1-31

A manufacturing process for NMOS silicon-gate ICs (Integrated Circuit Engineering Company).

# CHAPTER 2

## **TECHNOLOGY**

#### 2.0 INTRODUCTION

A good understanding of processing and fabrication technology on the part of the circuit designer is necessary to provide the flexibility needed to optimize integrated circuit designs. With this knowledge the actual layout can be considered during design and the appropriate parasitics can be included in the analysis. Innovative techniques that improve performance often involve circuits or geometries that are dependent on and applicable to a particular process. Knowledge of processing characteristics enables the designer to make yield calculations during design and consider tradeoffs between yield, performance and design simplicity.

In this chapter processing technology is discussed from a qualitative view-point. This is followed by a detailed discussion of typical NMOS, CMOS, bipolar, thick film, and thin film processes. Most processes in industry can be viewed as either a straightforward variant or extension of these processes. These processes are summarized in the appendices of this chapter. Included in the appendices are process scenarios, graphical process descriptions, design rules, process parameters, and some computer simulation model parameters. These appendices should provide a useful reference for material that is presented in later chapters of this book. This chapter is concluded with a discussion of practical layout considerations and comments about some CAD tools that have become an integral part of the IC design process.

#### 2.1 IC PRODUCTION PROCESS

The major steps involved in producing integrated circuits are considered from a qualitative viewpoint in this section. These steps are used in the MOS and/or bipolar processes that will be discussed later in this chapter.

### 2.1.1 Processing Steps

CRYSTAL PREPARATION. The substrate of bipolar and MOS integrated circuits is generally a single crystal of silicon that is lightly doped with either n- or p-type impurities. The substrate serves both as the physical medium upon and within which the IC is built and as part of the electrical circuit itself. These crystals are sliced from large right-circular cylinders of crystalline silicon, which are carefully grown to lengths up to 2 m and which vary in diameter from 1 to several inches. The slices are typically 250  $\mu$  to 400  $\mu$  thick. From an electrical viewpoint much thinner slices would be acceptable; however, the thicker slices have been adopted because they are more practical to handle (less breakage) and are less likely to warp during processing. The size of the wafers has been increasing rapidly with time to allow for both large chips and a larger number of chips per wafer. As of 1989, many of the older processing lines were using 4 inch wafers, but the newer lines are typically using 5 and 6 inch wafers. The crystals are often cut so that the surface is oriented approximately in the <100> direction.

MASKING. IC masks are high-contrast (black on clear) photographic positives or negatives. They are used to selectively prevent light from striking a photosensitized wafer during the photolithographic process. The masks are typically made of glass covered with a thin film of opaque metal, although less costly and less durable emulsion masks are sometimes used. The masks are produced from a digitized description of the desired mask geometries. There are several different methods of generating the masks (called pattern generation) from the digitized circuit description. One method involves photographically reducing large copies of the desired patterns that have been generated with a computer-controlled drafting machine. This method was used widely in the past but has largely been replaced by the next two. A second uses a laser beam as a pattern generator in a raster-scan mode. Both of these methods generally also require a high-resolution step and repeat and/or reduction camera to make the final masks that will be used. The intermediate image that is created is called a reticle and is usually 5 or 10 times real size. A third method uses an electron beam (E-beam) to generate the actual patterns directly onto the final masks. This method produces the best quality masks and is used extensively for very small geometries, but it requires considerable time and expensive equipment.

**PHOTOLITHOGRAPHIC PROCESS.** Photoresist is a viscous liquid. It is applied in a thin, uniform layer (about 1  $\mu$  thick by spinning the wafer) to the entire surface of a wafer following cleaning. After application the photoresist is hardened by baking. The physical characteristics of the photoresist can be changed by exposure to light. The photoresist thus acts as a film emulsion and can be exposed by light through the transparent areas of a mask (either by contact printing or projection), by a projection of light through a reticle containing the same information (called direct step on wafer), or by an electron beam (E-beam) that scans the desired regions. Following exposure, the resist is developed to selectively remove the resist from unwanted areas. This step is often followed by another baking to further harden the remaining photoresist.

Both positive and negative photoresists are available. With negative photoresist the unexposed areas are removed during development, and with positive resist the exposed areas are removed. Negative resists are noted for being quite unaffected by etchants used in processing, but finer resolution can typically be obtained with positive resists. Photoresists serve as protective layers to many etchants and oxidizing agents, and as a barrier to ion implants.

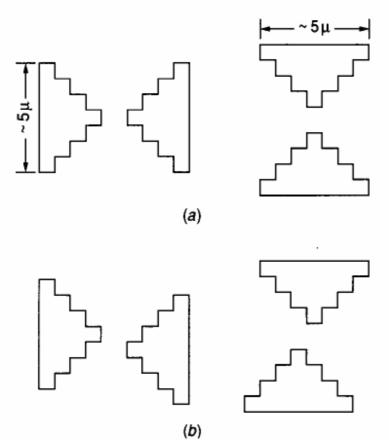

Proper mask alignment is essential to maintain device operation, characteristics, and yield. Alignment markings are generally included with the circuit information when the masks are made so that these marks will appear on the wafer during and after processing. A machine called a mask aligner is used to align and expose the wafers. Figure 2.1-1 shows typical alignment characteristics. The physical size and geometry of the masks used for fabrication is governed by the particular technique used by the mask aligner to expose the wafer. Mask aligners that use contact printing have multiple copies of the individual circuits at actual size (i.e., 1×) accurately patterned on the mask. These aligners have a large throughput and are relatively inexpensive. The large masks, however, have a very short lifetime (typically 3 to 10 exposures) because of damage incurred when the mask contacts the photoresist for exposure. This increases effective mask costs. The direct step on wafer aligners typically use a 5× mask (often called a reticle) as a negative. It typically will contain only a single copy of the circuit, though several copies may be used for small ICs. The image is optically reduced to 1× upon exposure. The wafer must be repeatedly moved to the next location after each exposure until the entire wafer is exposed. The lifetime of the mask is very long since no physical contact is made, but the throughput has been decreased considerably to allow for the successive wafer movements. The

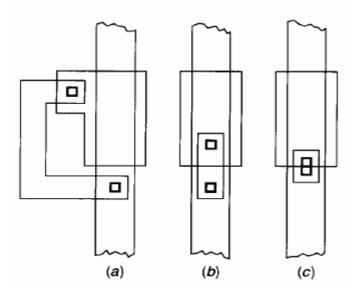

FIGURE 2.1-1

Alignment marks: (a) Mask marks, (b)

Simulated positioning of alignment marks after fabrication.

equipment is also considerably more expensive because of the precision needed to maintain consistent and repeated uniform stepping of the wafer. Both types of aligners are widely used in industry.

One of the most practical and popular methods of exposure actually combines the mechanical economics of the  $1 \times$  aligners and the mask life of the steppers. In this approach, a thin protective membrane, called a pelicle, is placed above the emulsion of  $1 \times$  chrome masks for protection of the mask and long mask life. Although the membrane itself may get dirty or scratched, it is placed far enough away from the mask so as to remain out of focus and thus not project defects onto the wafer when columniated light is focused through the mask onto the wafer.

A fourth method of exposure actually uses no masks at all. Instead, a narrow electron beam (E-beam) is selectively focused on the wafer in a raster-scan manner in small regions, with wafer stepping to position successive portions of the wafer under the beam. The same digital database that is used to generate masks can be used to drive the E-beam system. This approach gives better resolution than any of the previously discussed methods but involves very expensive equipment and has a much smaller throughput. It is practical for only the most demanding applications.

**DEPOSITION.** Films of various materials must be applied to the wafer during processing for most existing semiconductor processes. Often these films are very thin (200 Å or less for some  $SiO_2$  layers) but may be as thick as 20  $\mu$  for "thick film" circuits. Films that are deposited include insulators, resistive films, conductive films, dielectrics, n- and p-type semiconductor materials, and dopants that are subsequently forced deeper into the substrate. Deposition techniques include physical vapor deposition (evaporation and sputtering), chemical vapor deposition (CVD), and screen printing for the thick films. With the exception of the screen-printed films, the depositions are nonselective and are placed uniformly over the entire wafer.

Evaporation refers to evaporating the material that is to be deposited by controlling the temperature and pressure of the host material environment. A film is formed when the material condenses. A continuous evaporation—condensation process is established that allows for a controlled growth rate of the film.

Sputtering involves bombardment of the host material with high energy ions to dislodge molecules, which will reattach themselves to the surface of the wafer (as well as to other surfaces in the sputtering apparatus). Often two different host materials are simultaneously bombarded at different rates to establish the characteristics of the sputtered material. This dual host bombardment is termed cosputtering. With some materials, sputtering offers advantages over evaporation in host material integrity on the deposition surface.

Chemical vapor deposition (CVD) is achieved in two ways: (1) by causing a reaction of two gases near the substrate, a reaction occurs that creates solid molecules, which subsequently adhere to the substrate surface; or (2) by pyrolytic decomposition (a decomposition caused by heating) of a single gas, which also frees the desired molecules for reattachment.

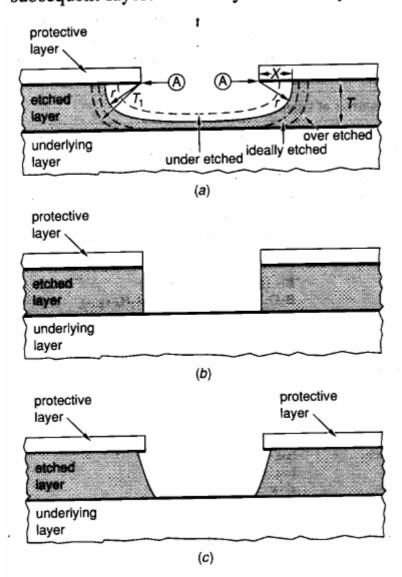

ETCHING. Etching refers to selectively removing unwanted material from the surface of the substrate. Photoresist and masks are used to selectively pattern (expose) the surface of the substrate. Following this patterning, the physical characteristics of the surface are changed by etching. A single IC will generally undergo several different etches during processing. The chemicals used for etching are chosen to selectively react with unprotected areas on the wafer while not affecting the protected areas. A summary of the effects of some commonly used etchants on typical semiconductor materials is shown in Table 2.1-1.

There are two types of etches used in production: wet and dry. The wet etches, often called chemical etches, use liquid etching agents, which are applied to the substrate surface. Although they have received widespread application in the past, they etch horizontally as well as vertically into the surface of the substrate. This horizontal etching causes undercutting of the patterned areas. Unless the width of the nonetched regions is orders of magnitude greater than the thickness of the material being etched, the nonuniformity of the horizontal etching causes significant changes in desired device characteristics.

TABLE 2.1-1 Characteristics of commonly used fabrication materials

| I. Materials used in IC fabrication                            |                                                                                   |                                                                                                                                                                                                               |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Purpose                                                        | Materials                                                                         | Comments                                                                                                                                                                                                      |  |

| Silicon crystal substrates                                     | SiCl <sub>4</sub>                                                                 | Silicon source for growth of single crystal silicon                                                                                                                                                           |  |

|                                                                | SiHCl <sub>4</sub>                                                                | Silicon source for growth of single<br>crystal silicon                                                                                                                                                        |  |

|                                                                | SiO <sub>2</sub> (Sand)                                                           | Silicon source for growth of single<br>crystal silicon                                                                                                                                                        |  |

| Silicon layers (both<br>single crystalline<br>and polysilicon) | SiCl <sub>4</sub> and H <sub>2</sub>                                              | The hydrogen gas strips the Cl atoms to form solid silicon.                                                                                                                                                   |  |

|                                                                | SiH <sub>4</sub>                                                                  | Heat causes the release (pyrolysis)                                                                                                                                                                           |  |

|                                                                | $SiH_2Cl_2$                                                                       | of H <sub>2</sub> gas.<br>Heat causes the release (pyrolysis)<br>of HCl gas.                                                                                                                                  |  |

| Oxides                                                         | O <sub>2</sub><br>H <sub>2</sub> O (Steam)<br>SiH <sub>4</sub> and O <sub>2</sub> | Used to grow SiO <sub>2</sub> by thermal oxidation<br>Used to grow SiO <sub>2</sub> by thermal oxidation<br>Used for CVD deposition of SiO <sub>2</sub><br>and to grow protective "glass" (SiO <sub>2</sub> ) |  |

| Nitride layers                                                 | Si <sub>4</sub> and NH <sub>3</sub>                                               | The ammonia causes the release of hydrogen gas and leaves Si <sub>3</sub> N <sub>4</sub> .                                                                                                                    |  |

|                                                                | SiCl <sub>4</sub> and NH <sub>3</sub>                                             | The ammonia causes the release of HCl and leaves Si <sub>3</sub> N <sub>4</sub> .                                                                                                                             |  |

| Etches, wet                                                    | HF                                                                                | Hydrofluoric acid etches SiO <sub>2</sub> but<br>not Si, Si <sub>3</sub> N <sub>4</sub> , or photoresist.                                                                                                     |  |

|                                                                | HF and HNO <sub>3</sub>                                                           | Etches Si                                                                                                                                                                                                     |  |

TABLE 2.1-1 (Continued)

| Purpose                                           | Materials                                                                                               | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                   | H <sub>3</sub> PO <sub>4</sub>                                                                          | Hot phosphoric acid etches Si <sub>3</sub> N <sub>4</sub> but                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                   |                                                                                                         | not SiO2. Removes some types                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                   |                                                                                                         | of photoresist.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Etches, dry                                       | $CHF_3$                                                                                                 | Etches SiO <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                   | $C_3F_8$                                                                                                | Etches SiO <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                   | SF <sub>6</sub>                                                                                         | Etches silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                   | CF <sub>4</sub>                                                                                         | Etches Si <sub>3</sub> N <sub>4</sub>                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   | CCl <sub>4</sub>                                                                                        | Etches aluminum                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Patterning                                        | Photoresist                                                                                             | Used as barrier to ion implants. Also used                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                   |                                                                                                         | to pattern SiO2 since photoresist is not                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                   |                                                                                                         | affected by HF, a common SiO2 etchant.                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                   | SiO <sub>2</sub>                                                                                        | Acts as a barrier to some p- and n-                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                   |                                                                                                         | type impurities                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                   | Si <sub>3</sub> N <sub>4</sub>                                                                          | Used as protective layer over silicon                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   |                                                                                                         | or SiO2 to prevent thermal growth                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                   |                                                                                                         | of SiO2. Also serves as a barrier to                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                   |                                                                                                         | low-energy ion implants although thin                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   |                                                                                                         | layers can be and are penetrated with                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   |                                                                                                         | higher-energy implants. Also serves                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                   |                                                                                                         | as a diffusion barrier to impurities                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                   |                                                                                                         | such as Ga, Al, Zn, and Na.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                   |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                   | II. Sources o                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                   | II. Sources o                                                                                           | f impurities Source                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| n-type                                            | Impurities  Arsenic                                                                                     | Source<br>As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                       |

| n-type                                            | Impurities  Arsenic Antimony                                                                            | Source $As_2O_3, AsH_3$ $Sb_2O_3, Sb_2O_4$                                                                                                                                                                                                                                                                                                                                                                                                                        |

| n-type                                            | Impurities  Arsenic                                                                                     | Source  As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—                                                                                                                                                                                                                                                       |

| n-type                                            | Impurities  Arsenic Antimony                                                                            | Source $As_2O_3, AsH_3$ $Sb_2O_3, Sb_2O_4$                                                                                                                                                                                                                                                                                                                                                                                                                        |

| n-type<br>p-type                                  | Arsenic<br>Antimony<br>Phosphorus<br>Gallium                                                            | Source  As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—                                                                                                                                                                                                                                                       |

|                                                   | Arsenic<br>Antimony<br>Phosphorus<br>Gallium<br>Aluminum                                                | Source  As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—implant or diffusion)                                                                                                                                                                                                                                  |

|                                                   | Arsenic<br>Antimony<br>Phosphorus<br>Gallium                                                            | Source  As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—implant or diffusion)  BN (solid), BBr <sub>3</sub> (liquid),                                                                                                                                                                                          |

|                                                   | Arsenic<br>Antimony<br>Phosphorus<br>Gallium<br>Aluminum                                                | Source  As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—implant or diffusion)  BN (solid), BBr <sub>3</sub> (liquid), B <sub>2</sub> O <sub>3</sub> (gas), BCl <sub>3</sub> , (gas), B <sub>2</sub> H <sub>6</sub> (gas),                                                                                      |

|                                                   | Arsenic<br>Antimony<br>Phosphorus<br>Gallium<br>Aluminum                                                | Source  As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—implant or diffusion)  BN (solid), BBr <sub>3</sub> (liquid),                                                                                                                                                                                          |

|                                                   | Arsenic<br>Antimony<br>Phosphorus<br>Gallium<br>Aluminum                                                | As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—implant or diffusion)  BN (solid), BBr <sub>3</sub> (liquid), B <sub>2</sub> O <sub>3</sub> (gas), BCl <sub>3</sub> , (gas), B <sub>2</sub> H <sub>6</sub> (gas), BF <sub>3</sub> (for implants)                                                               |

|                                                   | Arsenic<br>Antimony<br>Phosphorus<br>Gallium<br>Aluminum<br>Boron                                       | As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—implant or diffusion)  BN (solid), BBr <sub>3</sub> (liquid), B <sub>2</sub> O <sub>3</sub> (gas), BCl <sub>3</sub> , (gas), B <sub>2</sub> H <sub>6</sub> (gas), BF <sub>3</sub> (for implants)                                                               |

| p-type                                            | Impurities  Arsenic Antimony Phosphorus  Gallium Aluminum Boron  III. Impurity mig                      | As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—implant or diffusion)  BN (solid), BBr <sub>3</sub> (liquid), B <sub>2</sub> O <sub>3</sub> (gas), BCl <sub>3</sub> , (gas), B <sub>2</sub> H <sub>6</sub> (gas), BF <sub>3</sub> (for implants)                                                               |

| p-type<br>Impurity                                | Arsenic Antimony Phosphorus  Gallium Aluminum Boron  III. Impurity mig                                  | Source  As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—implant or diffusion)  BN (solid), BBr <sub>3</sub> (liquid), B <sub>2</sub> O <sub>3</sub> (gas), BCl <sub>3</sub> , (gas), B <sub>2</sub> H <sub>6</sub> (gas), BF <sub>3</sub> (for implants)  ration in silicon                                    |

| Impurity  Arsenic†(n) Antimony (n) Phosphorus (n) | Arsenic Antimony Phosphorus  Gallium Aluminum Boron  HII. Impurity mig Silicon moderate                 | As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—implant or diffusion)  BN (solid), BBr <sub>3</sub> (liquid), B <sub>2</sub> O <sub>3</sub> (gas), BCl <sub>3</sub> , (gas), B <sub>2</sub> H <sub>6</sub> (gas), BF <sub>3</sub> (for implants)  ration in silicon  SiO <sub>2</sub> very slow                |

| Impurity  Arsenic†(n) Antimony (n) Phosphorus (n) | Arsenic Antimony Phosphorus  Gallium Aluminum Boron  III. Impurity mig Silicon  moderate moderate       | As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—implant or diffusion)  BN (solid), BBr <sub>3</sub> (liquid), B <sub>2</sub> O <sub>3</sub> (gas), BCl <sub>3</sub> , (gas), B <sub>2</sub> H <sub>6</sub> (gas), BF <sub>3</sub> (for implants)  ration in silicon  SiO <sub>2</sub> very slow very slow      |

| p-type  Impurity  Arsenic†(n) Antimony (n)        | Arsenic Antimony Phosphorus  Gallium Aluminum Boron  HII. Impurity mig  Silicon  moderate moderate fast | As <sub>2</sub> O <sub>3</sub> , AsH <sub>3</sub> Sb <sub>2</sub> O <sub>3</sub> , Sb <sub>2</sub> O <sub>4</sub> P <sub>2</sub> O <sub>5</sub> , POCl <sub>3</sub> (liquid), PH <sub>3</sub> (gas—implant or diffusion)  BN (solid), BBr <sub>3</sub> (liquid), B <sub>2</sub> O <sub>3</sub> (gas), BCl <sub>3</sub> , (gas), B <sub>2</sub> H <sub>6</sub> (gas), BF <sub>3</sub> (for implants)  ration in silicon  SiO <sub>2</sub> very slow very slow slow |

<sup>†</sup>Arsenic is often preferred to the other n-type impurities because it gives more abrupt junction gradients, which yield better frequency response and improved current gain in bipolar transistors. Due to environmental concerns, however, the use of arsenic in the semiconductor industry is limited.

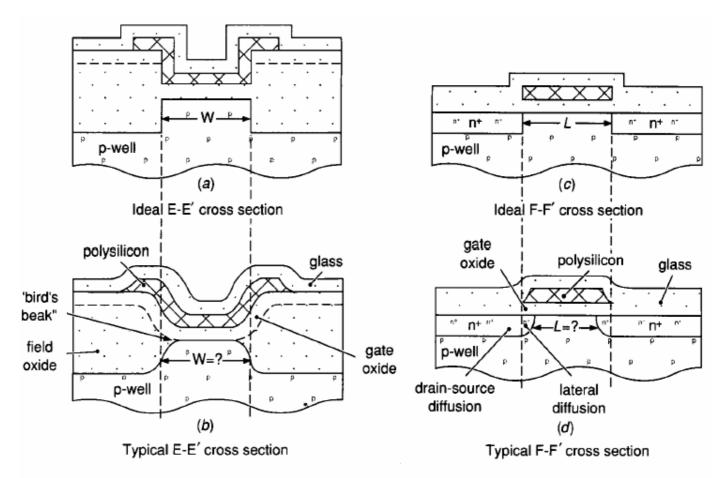

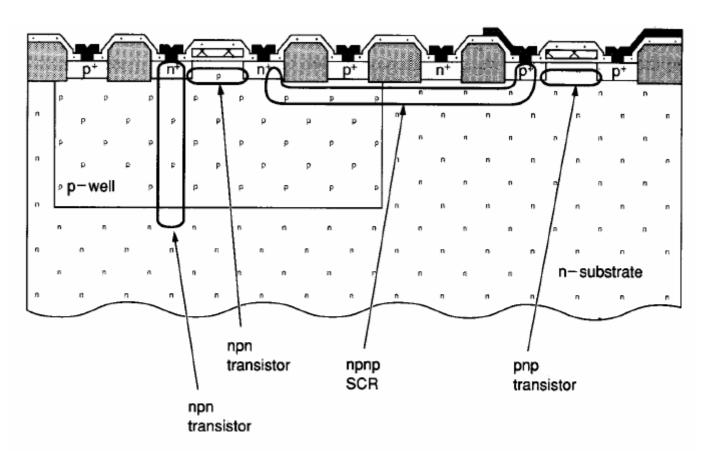

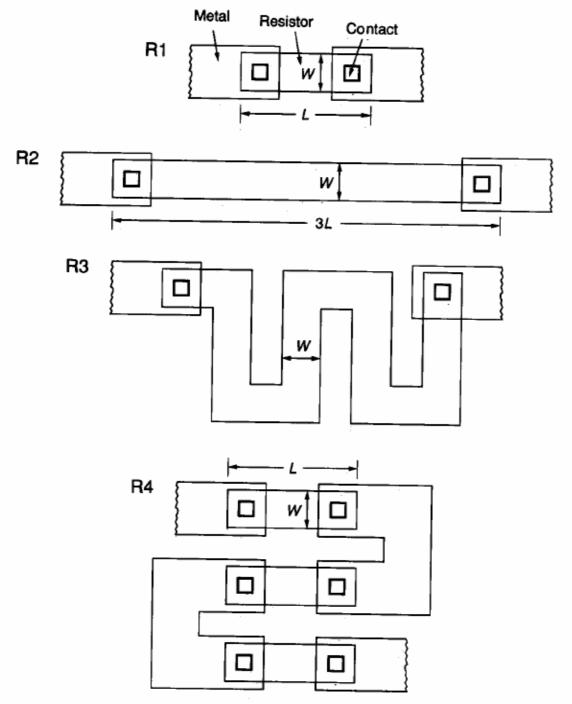

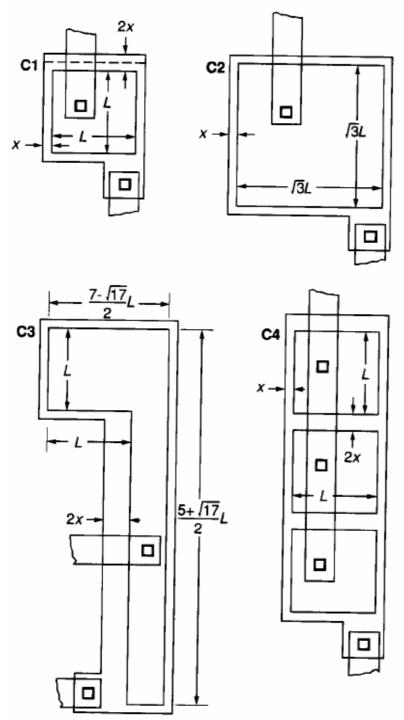

Dry etching, also termed ion etching, is directional and thus much less susceptible to the undesirable horizontal undercutting. Dry etching techniques include sputter etching, ion-beam etching, and plasma etching. Since no liquid chemicals are involved, a significant reduction of costs associated with disposal of spent chemicals is realized when dry etches are used. The etch rate for dry etches is generally lower than the wet etch rate. Dry etching is recognized as a practical alternative to wet etching and is widely used.